# To Design Logic Circuits by Using Symmetrical Coordinate

SHEN Yu

Research Institute of Remote Test and Control, Chongqing University of Technology, Chongqing, China E-mail: aliasxx@cqut.edu.cn

YU Cheng-Bo\*

Research Institute of Remote Test and Control, Chongqing University of Technology, Chongqing, China E-mail: yuchengbo@cqut.edu.cn

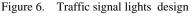

*Abstract*— Currently there has not been a single tool that could be used to design both the combined circuits and the time-sequential circuits. The symmetrical coordinate system stated in this article can be constructed to represent various states of multi-dimensional logical variables. Using the symmetrical coordinate system, it is not only possible to complete the design of combined circuits, but also to carry out all the procedures needed in the design of time-sequence circuits. Thus the combined circuits and the time-sequential circuits can be easily designed with a same design tool. Experiments are given in this article to illustrate how to use the system of symmetrical coordinate to design the logic circuits.

*Index Terms*—symmetrical coordinate; Logic circuit; Quadrants merge; Procedure diagram

## I. INTRODUCTION

How to design logical circuits is a topic often discussed in electro-technique field. Logical circuits may be divided into two classes-combined logical circuits (CLC) and time-sequential logical circuits (SLC). For the design of CLC, the researchers have recently emphasized on the simplification and combination of terms of the logical expression [1] [2] [3], and on the acceptance of different expressions to express different devices used [4] [5]. As for the design of SLC, some researchers have not only emphasized on the use of Karnaugh map [6] [7] [8], but also studied many aspects of the design such as the drawing of original state map [9], the simplification of the logic states [10], the relationships between the stateconverting map and various equations, expressions, and the HDL language [11] [12] [13]. All the researches mentioned above have in a certain degree improved and simplified the process in the design of logical circuits. However, limited by the methods used, these researches did not take together the CLC and the SLC in one design tool, and failed to have an overall plan for the whole process of the design of SLC with one tool. In this article,

the use of symmetrical coordinate system in the logic circuit design is introduced. Because all the elements needed in a logic circuit design, such as logic states, procedural flow chart, secondary Karnaugh map, the irrelevant terms and restraint terms, can be expressed in the symmetrical coordinate system, it is not only possible to complete the design of CLC with this system, but also to carry out all the procedures needed in the design of SLC, thus enable designers to complete both CLS and SLC designs using one tool.

# II. SYMMETRICAL COORDINATE

Symmetrical coordinate is a coordinate system indicating logic state with dual values. All variables in the coordinate have the logic value of either "1" or "0". The relationship among the logic values satisfies the specification of Boolean algebra. Each quadrant in the system is logically symmetrical [14].

Figure 1 shows the basic symmetrical coordinates from one-dimensional variable to three-dimensional variables.

Figure 1. basic symmetrical coordinates

<sup>\*</sup> YU Cheng-Bo: Corresponding author. Tel.: 86-23-68662239

Selected Best Papers of CCCM2009, Volume IV, Issue 2, pp. 5~9

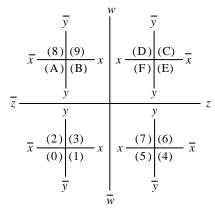

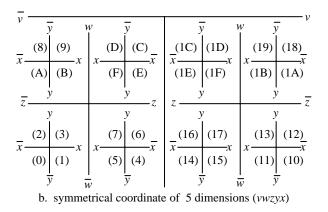

In the three-dimensional symmetrical coordinate, the quadrants on the left and the quadrants on the right are symmetrical. Based on this symmetrical relationship, the symmetrical coordinates for four-dimensional and five-dimensional variables can be constructed as shown in Figure 2.

In each quadrant, the variable has a value as a Hexadecimal number. Take quadrant (A) = (1010) for example: in the four-dimensional symmetrical coordinate, this quadrant has a value of (wzyx) = (1010); in the five-dimensional coordinate, this quadrant has a value of (vwzyx) = (01010). With this way more dimensional coordinates can be constructed.

In a symmetrical coordinate, each quadrant corresponds to a so-called "smallest logic item" in the logic expressions. Among every two "smallest logic item" in each pair of adjacent quadrants, there is one and only one variable that would change its value, so the adjacent quadrants in a symmetrical coordinate satisfy the definition of adjacency in logic functions. Thus the simplification operation of the logic expression can be conveniently and visually performed in the symmetrical coordinate.

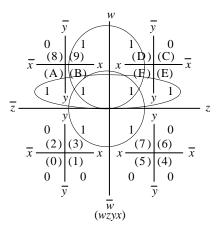

In a symmetrical coordinate, all the quadrants with f= "1" can indicate the function *f*. Figure 3 then shows a combined diagram for the logic function  $f=xy\overline{z}w+x\overline{y}zw+\overline{x}y\overline{z}w+xy\overline{z}w+xyzw+\overline{x}yzw+\overline{x}yz\overline{w}+xy\overline{z}\overline{w}$ .

a. symmetrical coordinate of 4 dimensions (*wzyx*)

Figure 2. symmetrical coordinate of 4 and 5 dimensions

Figure 3. simplify the expression with symmetrical coordinate

In the coordinate, the logic function can be simplified by directly merging the adjacent items as demonstrated with circles in Figure 3. Follow the circles in Figure 3, the expression of function can be simplified as:

# f = xw + yw + xy.

Because of these characteristics, the symmetrical coordinates can be used in logic circuit design. As stated before, logic circuit design can be divided as CLC design and SLC design. SLC design can be further divided into relay-type SLC design, and trigger-type SLC design. These three types of design will be discusses respectively below.

#### III. CLC DESIGN

The design of CLC can start by constructing a symmetrical coordinate with independent variables. Then write down the values of the function in the coordinate. The function expression would be the sum of the "smallest logic items" which have a function value of "1". For example, f = xw + xy + xw is the function for Figure 3.

**Experiment 1.** Design a circuit to control a lamp with three on-off switches at different locations. Each of the switches should be able to change the state of the lamp at any given time.

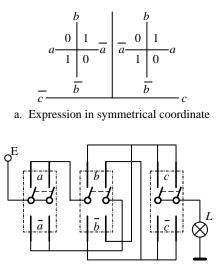

Solution: Label the three switches as a, b, c, and label the lamp as L. Make each switch as an axis in a three-dimensional symmetrical coordinate. Write down the L value of "1" and "0" alternately in the three-dimensional symmetrical coordinate as shown in Figure 4a.

The diagram of Figure 4a illustrates the condition of one-time state change of any of the three switches. The state of lamp (the function value) changes with the change of conditions. Based on Figure 4a, the function for lamp L=1 can be obtained:

$L = abc + a\overline{b}\,\overline{c} + \overline{a}b\overline{c} + \overline{a}\overline{b}\,c = a(bc + \overline{b}\,\overline{c}) + \overline{a}(b\overline{c} + \overline{b}\,c)$

Take three on-off switches and one lamp, make wire connections according to this function and the circuit is then obtained as shown in Figure 4b.

b. Electronic circuit

Figure 4. Control a lamp with three switches

## IV. RELAY-TYPE SLC DESIGN

Since there is a mutual-constraining relationship among the variables in SLC, the SLC design needs to have almost every variable's function expression. To design a SLC, first draw a time-sequence procedural flow diagram directly in the symmetrical coordinate, then handle each specific time sequence variable individually. When handling a specific time sequence variable, first find the ending quadrant of the sequence where the variable equals "1", and then track back to the starting quadrant and get the "smallest logic item". The variable function is then obtained as the sum of all these "smallest logic items". When writing the function expression, it is very easy to simplify the expression since the irrelevant and constraint items are all in the symmetrical coordinate.

**Experiment 2.** To control a motor M with three buttons A, B, and C. A is the forward rotation button. Motor M rotates forward when A is pressed. B is the backward rotation button, when B is pressed, Motor M rotates backward. C is the stop button, when C is pressed, Motor M stops rotation.

There are three states of the Motor to be remembered – forward, backward, and stop, so two relays Y and Z are chosen. Y controls Motor forward rotation, Z controls motor backward rotation. Together with the three buttons, there are five logic variables. A, B, C are independent variables, and Y and Z are dependent variables. Let "0" indicate normal state, and "1" indicate action state.

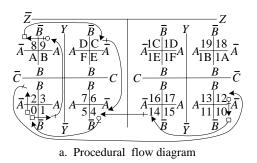

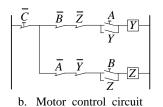

Figure 5a shows the procedural flow diagram of this control project. There are two possibly closed circulation flows - forward and backward rotations. Arrows are used in the diagrams to indicate the action of each time sequence. At the start of the arrow line, a square is drawn to indicate an external force initiating an action, and a circle drawn to indicate the external force was withdrawn. A cross drawn at the start of the arrow line indicates a generated action.

Figure 5. Design a controller for motor rotation in two diversity direction

In the procedural diagram, the quadrant Y=1 has m9, m8 and mC(in Figure 5a, the quadrants labeled 9,8 and C), the previous states are m1, m9 and m8 respectively, thus the function for dependent variable Y is obtained as follows:

$$Y^{n+1} = m_1 + m_9 + m_8 = (m_1 + m_9) + (m_9 + m_8)$$

$$= \overline{Z} \cdot \overline{C} \cdot \overline{B} \cdot A + \overline{Z} \cdot Y \cdot \overline{C} \cdot \overline{B}$$

$$= \overline{Z} \cdot \overline{C} \cdot \overline{B} \cdot (A + Y)$$

The same way, the function for dependent variable *Z* obtained:

$$Z^{n+1} = m_2 + m_{12} + m_{10} = (m_2 + m_{12}) + (m_{12} + m_{10})$$

$$= \overline{Y} \cdot \overline{C} \cdot B \cdot \overline{A} + Z \cdot \overline{Y} \cdot \overline{C} \cdot \overline{A}$$

$$= \overline{Y} \cdot \overline{C} \cdot \overline{A} \cdot (B + Z)$$

Based on these functions, the logic control circuit for the motor control project is obtained as shown in Figure 5b.

When designing SLC, it can be considered to use the memory components only as the axis in the symmetric coordinate since the circuit states are determined only by the memory components. In the above experiment, the buttons A, B and C do not have to be the axis in the symmetrical coordinate instead they can be listed as the condition of certain state. This method sometimes can simplify the solution.

For example, for those logic circuits with time-delay controllers, a square can be drawn to indicate the timedelay condition at the start of the arrow line in the diagram. In this case, when considering the variables' functions, not only the prior state of the value "1" quadrant needs to be considered, but the state and condition when the action entering and leaving the quadrant also need to be considered.

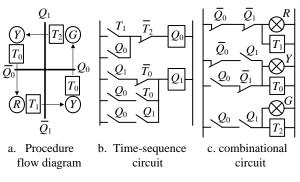

**Experiment 3.** Three traffic signal lights  $- \operatorname{Red}(R)$ , Yellow(*Y*) and Green(*G*) -are turned on and off alternately without interruption in the order of *R*-*Y*-*G*-*Y*-*R*...... The on-time for the Yellow light is controlled by

$T_0$ , the on-time for the Red light is controlled by  $T_1$ , and the on-time for the Green light is controlled by  $T_2$ .

The time sequence for the three traffic lights' on-time circulates with four states as R-Y-G-Y. Two memory devices  $Q_0$  and  $Q_1$  can be used for these four states.

Figure 6a depicts the traffic lights flow diagram in a symmetrical coordinate. The dependent variables in each quadrant are indicated with circles. The conditions for the timing device are marked in the squares in the starting quadrants.

In the symmetrical coordinate diagram, the quadrant  $Q_0=1$  is on the right side. Its prior state is in the two quadrants at the lower part of the coordinate. The quadrant  $Q_1=1$  is on the upper portion of the coordinate. Its prior state is in the two quadrants on the right side of the coordinate. The functions are then obtained as follows:

$$\begin{aligned} Q_0^{n+1} &= Q_0 \cdot Q_1 \cdot T_1 + Q_0 \cdot Q_1 \cdot T_0 \\ Q_1^{n+1} &= Q_0 \cdot \overline{Q_1} \cdot T_0 + Q_0 \cdot Q_1 \cdot T_2 \\ R &= T_1 = \overline{Q_0} \cdot \overline{Q_1} \\ Y &= T_0 = \overline{Q_0} \cdot Q_1 + Q_0 \cdot \overline{Q_1} \\ G &= T_2 = Q_0 \cdot Q_1 \end{aligned}$$

The first two functions are time-sequence logic functions, the latter three functions are combinational logic functions. Based on these five functions, the traffic signal lights control circuit is constructed as shown in Figures 6b and 6c.

The above two experiments demonstrate the design of relay-type SLC. Note that when drawing the flow diagram for relay-type SLC, the starting and ending quadrants of each flow procedure should be restricted to the adjacent quadrants. This is required by the property of the relay devices.

Now we take a real machine circuit design as an example.

**Experiment 4.** The manipulator of a NC milling machine is used to exchange cutting tools between the knife-store and the machine. It has an arm with two knife-holders (one for new and one for old) on the outside end. The arm can be lengthened or shortened when needed. The holders are symmetrically arranged so that they can exchange positions when the arm turns round a half revolution. The body of the manipulator can rotate from knife store to the principal axis of the machine, and vice versa.

Besides this, a locator and a knife tighter are employed to locate the knife just needed in the store, and to tighten the new knife inserted in the machine respectively. Of course, a device for pulling out the knife from and inserting it into the store and machine is also necessary.

The sequence of action of the manipulator is as follows. Take the situation as the starting state (step 0) when the body has just rotated to the store, while the inserter and tighter still in the acting state. Then the locator comes on (step 1) to make sure that when the arm stretches out, the empty holder will be just opposite to the new cutting tool needed, while the other holder has had an old tool in it. Then the arm stretches (step 2) and pulls the tool out of the store (step 3) and inserts it into the holder. The arm will draw back now (step 4) so it can turn round half a revolution (step 5). After turning, the arm stretches again (step 6), then the holder for old tool will come to position and the tool it held can be inserted (step 7) into the store. The arm draws back again (step 8). Then the locator goes off (step 9). The exchange of tools in store side is completed now. Then the body rotates back to the principal axis (step 10), and the arm stretches (step11). The tighter will now serve to loosen the tool on the machine (step 12). After this is done, the tool is pulled out (step13) from the machine into the holder. On this side, it is unnecessary to draw the arm back to enable the turning of arm. So the arm turns round half a revolution (step14). Then the new knife is inserted (step 15) in the machine and will be tightened by the tighter (step 16). Now the arm draws back (step 17). The body rotates from the machine to knife store-side, back to the starting state (step 0), thus completing a circulating cycle.

In designing the control circuit to fulfill the above actions, six variables are needed, shown in Table 1.

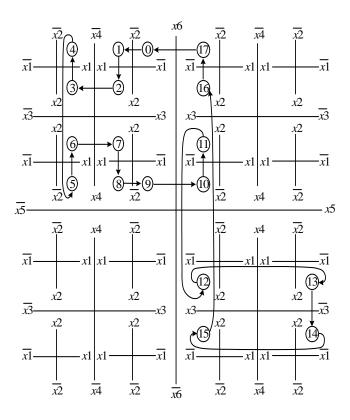

Now, draw the system of symmetrical quarters for 6 variables as shown in Figure 7.

According to the sequence of action described above, draw the traverse diagram on the system. From step 0 to step 17, it has 18 steps in Figure 7.

| Variable   | Stands for         | Takes value 1<br>as   | Takes value 0<br>as   |

|------------|--------------------|-----------------------|-----------------------|

| <i>X</i> 1 | Locator            | Come on               | Go off                |

| X2         | Arm<br>stretching  | Lengthen              | Shorten               |

| X3         | Knife<br>inserting | Insert into           | Pull out              |

| <i>X</i> 4 | Arm<br>turning     | Old tool at site      | New tool at site      |

| X5         | Body<br>rotating   | From store to machine | From machine to store |

| <i>X</i> 6 | Knife<br>tighter   | Tighten the tool      | Loosen the tool       |

TABLE I.

Variables of manipulator of a NC milling machine

Figure 7. Symmetrical quarters of manipulator of a NC milling machine

According to Figure 7, Table II shows the six variables' step where their value equals to "1", and then track back to the starting quadrant, the previous step number. and their combination shown in Table II. According to the combination of the step numbers, the expressions of the variables' function are shown in the right column of table II.

The void quarters in Figure 7 have been used in the functions of Table II. For example, the quarters step numbered (0, 1, 2, 3, 4), when the void quarters  $\overline{x}_1 x_2 x_3 \overline{x}_4 \overline{x}_5 x_6$ ,  $\overline{x}_1 x_2 \overline{x}_3 \overline{x}_4 \overline{x}_5 x_6$  and  $\overline{x}_1 \overline{x}_2 \overline{x}_3 \overline{x}_4 \overline{x}_5 x_6$  used, its expression is  $\overline{x}_4 \overline{x}_5 x_6$ ; but when the symmetrical 8 void quarters in  $\overline{x}_6$  used, the expression is changed to  $\overline{x}_4 \overline{x}_5$ . The expressions of X's function are used void quarters as the same methods.

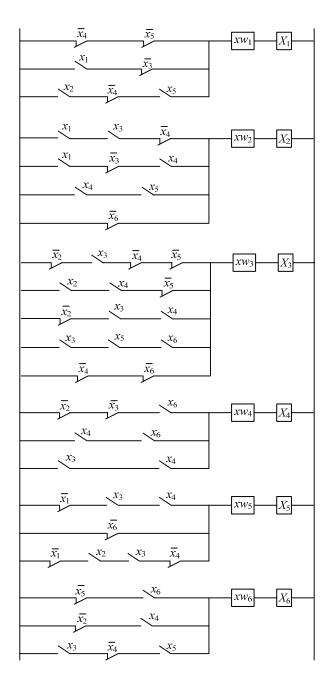

According to Table II, Figure 8 shows the basic circles for the manipulator of the NC milling machine.

Practically, in the course of circulation, some external factors should be inserted in, and they must be considered in the input expression of relevant variable. As a whole control system of the manipulator, some other auxiliary circuits are also needed, the  $xw_1$  to  $xw_6$  in Figure 8 are the auxiliary elements. The contents of  $xw_i$  is beyond the scope of our present work, and will not be discussed here.

| Basis variables' value for Figure 7 |                                                    |                                                       |                                                                 |                                                                                                                                                    |  |

|-------------------------------------|----------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Variabl<br>e                        | Step No. for variable equals "1"                   | the previous step<br>No.                              | Combination of the step No.                                     | Expression of <i>X</i> 's function                                                                                                                 |  |

| <i>X</i> 1                          | 1, 2, 3, 4, 5,<br>6, 7, 8                          | 0, 1, 2, 3,<br>4, 5, 6, 7                             | (0, 1, 2, 3,<br>4), (3, 4, 5,<br>6), (6, 7)                     | $\overline{x}_4\overline{x}_5 + x_1\overline{x}_3 + x_2\overline{x}_4x_5$                                                                          |  |

| X2                                  | 2, 3, 6, 7,<br>11, 12, 13,<br>14, 15, 16           | 1, 2, 5, 6,<br>10, 11, 12,<br>13, 14, 15              | (1, 2), (5, 6),<br>(10, 11, 12,<br>13), (12, 13,<br>14, 15)     | $x_1 x_3 \overline{x}_4 + x_1 \overline{x}_3 x_4 + x_4 x_5 + \overline{x}_6$                                                                       |  |

| X3                                  | 0, 1, 2, 7, 8,<br>9, 10, 11, 12,<br>15, 16, 17     | 0, 1, 6, 7,<br>8, 9, 10, 11,<br>14, 15, 16, 17        | (0, 1), (6, 7),<br>(8, 9, 10), (10,<br>11, 16, 17),<br>(14, 15) | $\overline{x}_2 x_3 \overline{x}_4 \overline{x}_5 + x_2 x_4 \overline{x}_5 + \overline{x}_2 x_3 x_4 + x_3 x_5 x_6 + \overline{x}_4 \overline{x}_6$ |  |

| <i>X</i> 4                          | 5, 6, 7, 8, 9,<br>10, 11, 12, 13                   | 4, 5, 6, 7,<br>8, 9, 10, 11,<br>12                    | (4, 5), (5, 6,<br>7, 8, 9, 10,<br>11), (7, 8, 9,<br>10, 11, 12) | $\overline{x}_2\overline{x}_3x_6 + x_4x_6 + x_3x_4$                                                                                                |  |

| <i>X</i> 5                          | 10, 11, 12,<br>13, 14, 15,<br>16, 17               | 9, 10, 11,<br>12, 13, 14,<br>15, 16                   | (9, 10, 11,<br>12), (12, 13,<br>14, 15), (15, 16)               | $\overline{x}_1 x_3 x_4 + \overline{x}_6 + \overline{x}_1 x_2 x_3 \overline{x}_4$                                                                  |  |

| <i>X</i> 6                          | 0, 1, 2, 3, 4,<br>5, 6, 7, 8, 9,<br>10, 11, 16, 17 | 0, 1, 2, 3,<br>4, 5, 6, 7,<br>8, 9, 10, 15,<br>16, 17 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$            | $\overline{x}_5 x_6 + \overline{x}_2 x_4 + x_3 \overline{x}_4 x_5$                                                                                 |  |

TABLE II. Basis variables' value for Figure 7

Figure 8. basic circles of the NC milling machine

#### V. TRIGGER-TYPE SLC DESIGN

Trigger devices have clock input terminals. The trigger-type SLC includes various SSI triggers, and also includes various MSI shift registers, counters, and pulse distribution devices, etc., all with clock input.

Under the impact of the clock pulse, the triggers at various levels inside the logic chips can be enacted simultaneously, resulting in multiple state changes at the same time. In the symmetrical coordinate, each flow line in the diagram is no longer required to be at the adjacent quadrants as for the relay type circuit design. This is the difference in the designs between the trigger-type and relay-type in SLC.

**Experiment 5.** This is a project studied in [15]. Design a control circuit for an automatic soft-drink vending machine. The money taking slot only accepts 50-fen or one-Yuan coin. If the machine gets 1.50 Yuan, it gives out a soft drink. If the machine gets two one-Yuan coins, it gives out a soft drink and a 50-fen coin as change [15].

Use A=1 to indicate a one-Yuan coin, B=1 to indicate a 50-fen coin. Use Y and Z to indicate the machine giving out a soft drink and money change respectively.

In a normal situation, when a coin is inserted, the signal A=1 or B=1 is triggered. The trigger will automatically vanish after the circuit changes to a new state.

Solution: Since triggering signal twice (either *A* twice or *A* and *B* each one) can achieve the goal, or triggering signal *B* three times can also achieve the goal,  $1 < \log_2 3 < 2$ , two memory devices  $Q_0$  and  $Q_1$  are required. *Y* and *Z* are not involved in input and they are treated as CLC.

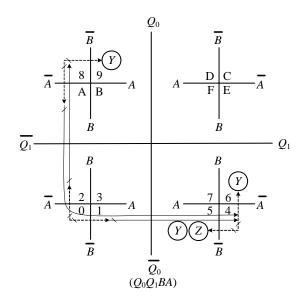

Let  $Q_1Q_0=00$  indicates the initial state,  $Q_1Q_0=01$  indicates a 50-fen coin is inserted, and  $Q_1Q_0 = 10$  indicates a total of one Yuan has accumulated. The state change diagram can be depicted in the  $Q_0Q_1$  symmetrical coordinate as shown in Figure 9.

The use of arrows in the diagram in Figure 7 is the same as in the previous experiments. However, the starting and ending points of the arrows are no longer restricted to the adjacent quadrants.

So when tracking the prior state of a value="1" quadrant, it is no longer limited to the adjacent quadrants. Following the state change diagram, the functions for the time-sequence variables  $Q_0$ ,  $Q_1$  and the output variables Y and Z can be easily obtained. Please note that in the state change diagram in the symmetrical coordinate, all the quadrants, except those with starting and ending point of arrows, can be treated as irrelevant items. The functions are then obtained as follows:

$$Q_{0} = m_{2} + m_{8} = (m_{2} + m_{3}) + (m_{8} + m_{C})$$

$$= \overline{Q_{1}} \cdot \overline{Q_{0}} \cdot B + Q_{0} \cdot \overline{A} \cdot \overline{B}$$

$$Q_{1} = m_{1} + m_{4} + m_{A}$$

$$= (m_{1} + m_{3}) + (m_{4} + m_{C}) + (m_{A} + m_{B} + m_{E} + m_{F})$$

$$= \overline{Q_{1}} \cdot \overline{Q_{0}} \cdot A + Q_{1} \cdot \overline{A} \cdot \overline{B} + Q_{0} \cdot B$$

$$Y = m_{5} + m_{6} + m_{9}$$

$$= (m_{5} + m_{7} + m_{F} + m_{D}) + (m_{6} + m_{7} + m_{F} + m_{E})$$

$$+ (m_{9} + m_{B} + m_{D} + m_{F})$$

$$= Q_{1}A + Q_{1}B + Q_{0}A$$

$$Z = m_5 = (m_5 + m_7 + m_F + m_D) = Q_1 A$$

Figure 9. Vending machine procedure flow diagram

Note the items within the parentheses in the above functions; it is very easy to simplify the expressions with the symmetrical coordinate in Figure 9.

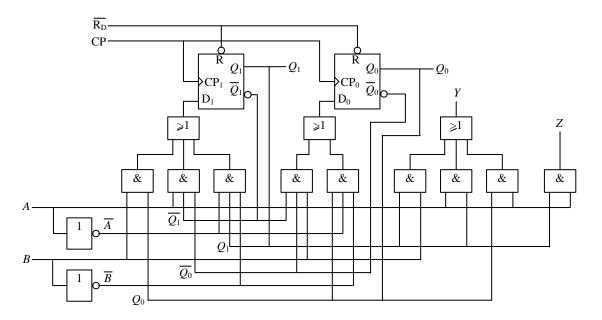

We have now obtained the control circuit as shown in Figure 10. This control circuit is the same circuit as described in References [15], but the method used here is much simpler.

# VI. CONCLUSION

Because of the symmetrical and visual character of the symmetrical coordinate system, it can be used as a very valuable tool in the design of CLC and also in the whole process of the design of SLC. Use the symmetrical coordinate system in the design of CLC, the logic terms can be unified and simplified directly in the coordinate system, thus making the design of CLC easy and simple. Use the symmetrical coordinate system in the design of SLC, the procedural flow can be directly charted in the coordinate system, and the prior-states of those value= "1" variables can be tracked and found easily in the system, and all the states of triggers that have impact on the SLC can be expressed in the system thus visualize and simplify the design of SLC, making it as easy and simple as that of CLC.

When a logic circuit has a large number of variables (e.g. greater than 9), the symmetrical coordinate could become enormous. In this case, we need to treat it in segment with computers, and some algorithm to handle it can also be used, which is beyond the scope of this article.

Figure 10. Control circuit for the vending machine

#### REFERENCES

- Tong Yu, Ke Zongwu, Hong Jiaping, "Design Methods for Combinational Logic Circuits," Journal of Hubei Normal University (Natural Science), vol. 25, no. 1, 2005, pp. 44-46

- Feng Naiqin, Sun Yuqiang, Wei Shutao, Chen Guanglin, "Research about Simplication Methods of Logical Function," Mini-Micro Computer Systems, vol. 24, no. 1, Jan. 2003, pp. 130-134

- [3] Liu Hongzhong, Wang Xinmin, Liu Haifeng, "Methods of Simplifying Logical Electric Circuit," Journal of Hebei University (Natural Science Edition), vol. 24, no.3, 2004, pp. 307-310

- [4] Nai Yihan, "Design of Combined Logic Circuits based on X\_OR Gates," Journal of Longyan University, vol. 24, no.3, 2006, pp. 21-24

- [5] Hong Shaochun, "Improve the Design of Mid-Scaled Combined Logical Circuits in Engineering Projects," Journal of Quanzhou Normal University (Natural Science), vol. 22, no.4, 2004, pp. 31-35

- [6] Xu Yongqian, Wan Yan, "Analysis of the Design Methods for Time-Sequence Circuits," Science and Technology Innovation Herald, 2008. no.10, pp. 61-62

- [7] Zhang Yunpeng, "The Design of Relay Control Circuits," Water Conservancy Science and Technology and Economy, vol. 14, no. 10, Oct. 2008, pp. 815-816

- [8] Xing Desheng, "The Application of Karnaugh Map in the Logical Function Transformation and MSI Logic Circuit Design," Journal of Jining Teachers College, vol. 29, no.4, 2007, pp. 46-49

- [9] Deng Yuanqing, "Design of Synchronous Sequential Circuits," Collection of Papers Presented at the 2008 Annual Conference of Association of Electronic Higher Education, Wuhan, 2008, pp. 168-171, unpublished

- [10] Xu Bing, "Study on the State Simplication Methods in Synchronous Sequential Circuits Design," Journal of Changji College, no.1, 2004, pp. 119-122

- [11] Shao Yuqin, Wang Lihua, Liu Zhijun, "Implementation of ASM Charts in Hardware Circuits in Logic Design," Science Journal of Teachers' College and University, vol. 26, no.1, 2006, pp. 36-38

- [12] Xu Sicheng, "New Methods in the Design of Synchronous Sequential Logic Circuits," Physics Experiments, vol. 24, no.11, 2004, pp. 9-11

- [13] Wu Hengyu, Tang Minli, "Application of Minor State of Karnaugh in rhe Time Sequence Logical Circuit of," Journal of Nanjing Institute of Industrial Technology, vol. 6, no.2, 2006, pp. 71-73

- [14] Shen Xiaofeng, Yu Lan, Shen Yu, Logic Algebra. Beijing: Science Press. pp. 79–81, Jan. 2008.

- [15] Yan Shi, Digital Electronic Technology Fundamentals. Beijing: Higher Education Press. 4th ed., pp. 283–286, Nov. 1998

Shen Yu is currently pursing her Master degree in signal and information processing at Research Institute of Remote Test and Control, Chongqing University of Technology. Her main research interests are in information acquisition and processing, wireless sensor networks. She was

born in 1984 in Wuhan, Hubei, China

Yu Cheng-Bo is currently Professor in the College of Electronic Information and Automation at Chongqing University of Technology. Dr. Yu is also the Director of Research Institute of Remote Test and Control at Chongqing University of technology. His main research interests are in

information acquisition and processing, remote test and control, and vehicle electronic technology.